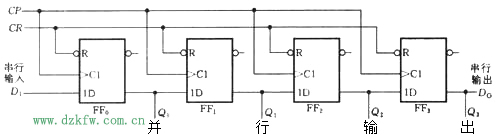

图1 用边沿D触发器构成的4位移位寄存器

|

表1 图1电路的状态表 | ||||||||||||||||||||||||||||||

|

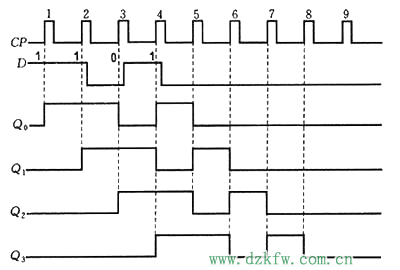

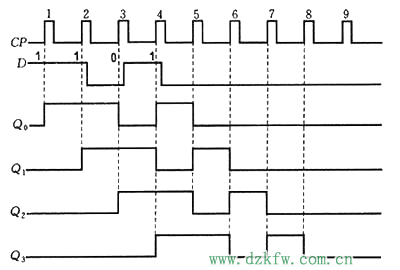

由表可知,输入数码依次地由低位触发器移到高位触发器,作右向移动。经过4个时钟脉冲后,4个触发器的输出状态Q3Q2Q1Q0与输入数码D3D2D1D0相对应。为了加深理解,在图2中画出了数码1101(相当于D3=1,D2=1,D1=0 ,D0=1)在寄存器中移位的波形,经过了4个时钟脉冲后,1101出现在寄存器的输出端Q3Q2Q1Q0。这样,就可将串行输入(从D1端输入)的数码转换为并行输出(从Q3、Q2、Q1、Q0端输出)的数码。这种转换方式特别适用于将接收到的串行输入信号转换为并行输出信号,以便于打印或由计算机处理。

图2 图1电路的时序图

在图3中还画出了第5到第8个时钟脉冲作用下,输入数码在寄存器中移位的波形(如图2所示)。由图可见,在第8个时钟脉冲作用后,数码从Q3端已全部移出寄存器。这说明存入该寄存器中的数码也可以从Q端串行输出。根据需要,可用更多的触发器组成多位移位寄存器。

除了用边沿D 触发器外,还可用其他类型的触发器来组成移位寄存器,例如,用主从JK 触发器来组成移位寄存器,其级间连接方式如图3所示。根据JK触发器的特征方程,由图3可得:

在图3中还画出了第5到第8个时钟脉冲作用下,输入数码在寄存器中移位的波形(如图2所示)。由图可见,在第8个时钟脉冲作用后,数码从Q3端已全部移出寄存器。这说明存入该寄存器中的数码也可以从Q端串行输出。根据需要,可用更多的触发器组成多位移位寄存器。

除了用边沿D 触发器外,还可用其他类型的触发器来组成移位寄存器,例如,用主从JK 触发器来组成移位寄存器,其级间连接方式如图3所示。根据JK触发器的特征方程,由图3可得:

FF2和FF3的接法与FF1完全相似,所以各JK 触发器均以D 触发器的功能工作,图3和图1所示电路具有相同的功能。

返回顶部

返回顶部 刷新页面

刷新页面 下到页底

下到页底